The BoW (Bunch of Wires) PHY layer is the physical foundation for communication between chiplets in a multi-chiplet design (ODSA) using the BoW interface. The BoW PHY layer is responsible for transmitting and receiving data signals between chiplets on the same package. The BoW PHY is defined as a single unidirectional slice. Multiple slices are combined to create links of the desired throughput.

BoW Modes

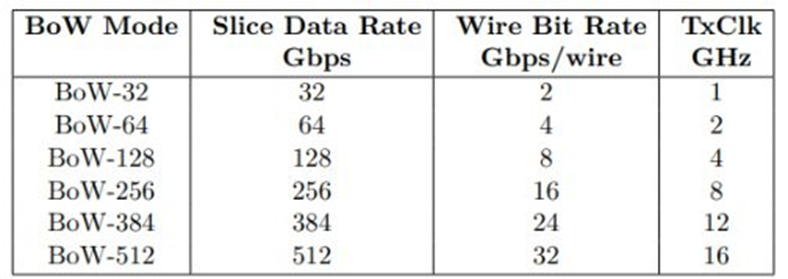

A BoW PHY must be operable in one of the BoW Modes. A BoW Mode defines the speed of clock and data of the PHY on the die-to-die wires.

BoW PHY Components

- Data Wires: A defined number of data wires (typically 16) carry the actual data payload.

- Differential Clock: A high-speed clock signal synchronized with the transmitter (TX) to help the receiver (RX) synchronize and interpret the data on the data wires.

- Optional Signals: Error Correction (FEC) and Auxiliary (AUX) signals can be included for enhanced reliability and additional functionalities.

BoW PHY Features

Scalability and Flexibility:

- Packaging Versatility: Works effectively with both organic laminate and advanced packaging technologies.

- Bump Placement Optimization: While the specification dictates data wire order, it allows some flexibility in bump placement during chip design, enabling some application-specific customization.

Power Saving Mechanisms:

- Data Idle State: When data isn’t actively flowing, data lines transition to a specific voltage level (often logic 0) to minimize power consumption.

- Clock Gated State: During data inactivity periods, the clock signal transmission halts completely. Preamble and postamble sequences are inserted into the data stream to ensure smooth data transmission resumption.

Open Standard and Interoperability:

- Developed by Open Compute Project (OCP): Being an open standard ensures chiplets from different vendors adhering to the BoW specification can work together on a single package, fostering innovation and competition within the chiplet ecosystem.

Additional Highlights:

- Simple Signaling: Leverages single-ended signaling instead of complex SerDes (serializer/deserializer) interfaces, reducing complexity and enabling denser wire packing.

- Error Correction and Auxiliary Signals (Optional): For enhanced reliability and additional functionalities, error correction (FEC) and auxiliary (AUX) signals can be incorporated.

More Information:

- Bunch of Wires (BoW) PHY specification : https://www.opencompute.org/documents/bow- specification-v2-0d-1-pdf

- The Bunch of Wires (BoW) : https://eps.ieee.org/images/files/TC_The_Bunch_of_Wires_rev3.pdf

- Die to Die Interconnects using BoW : https://semiwiki.com/ip/blue-cheetah-analog- design/317321-die-to-die-interconnects-using-bunch-of-wires-bow/