Introduction

For many years, semiconductor design followed a predictable pattern: create a big monolithic System-on-Chip (SoC) and link it to the rest of the system using well-known interconnect protocols. This technique was effective as long as transistor growth resulted in predictable gains in performance, power efficiency, and cost.

Today, that model is evolving. Modern processors are increasingly developed with chiplet-based designs, which combine numerous smaller dies into a single package to act as a single device. This change is being pushed by yield considerations, manufacturing limitations, power restrictions, and the increased need for heterogeneous integration. As a result, how different sections of a CPU interact has become an important architectural choice.

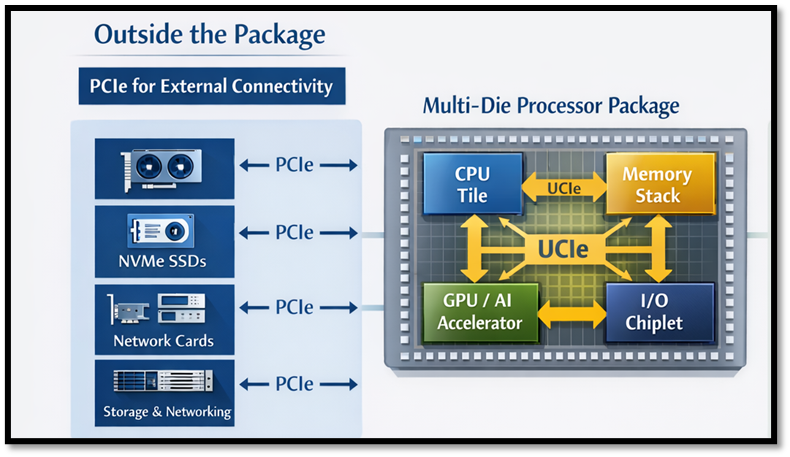

This development has resulted in a distinct division of roles: PCIe is intended for communication outside the package, whereas UCIe is meant for communication within the box. Understanding why this divide occurs is critical to predicting the future of semiconductor design.

Why Chiplet Architectures Changed Interconnect Requirements?

In a monolithic SoC, functional blocks communicate via on-die interconnects, which have exceptionally low latency and great bandwidth. When a design is divided into chiplets, the same communication must now transcend physical borders between different silicon dies. Even though these dies are integrated within the same package, the communication needs remain exceedingly high.

Inside a package, connectivity must emphasize bandwidth density, low latency, and energy efficiency above long-range resilience. Using an interconnect designed for board-level communication in this context adds additional complexity and inefficiency. This shift in physical and architectural restrictions rendered standard connectivity techniques ineffective for chiplet-based systems.

Why PCIe Works So Well Outside the Package

PCI Express (PCIe) remains the leading interconnect for system-level connection, and its success is anchored in its design objectives. PCIe is designed to function over lengthy motherboard traces, connections, and a wide range of electrical conditions while ensuring durability and compatibility between manufacturers and generations. These features make PCIe an excellent choice for linking CPUs to external components like as GPUs, SSDs, network interface cards, and accelerators.

Using PCIe inside the packaging would result in greater latency, more power consumption, and inefficient bandwidth use. Chiplet-to-chiplet communication necessitates a lightweight, high-efficiency connection that eliminates long-distance assumptions and concentrates solely on short-range performance. This mismatch demonstrates why, despite its advantages, PCIe is not appropriate for intra-package communication.

UCIe: Designed Specifically for Chiplet Communication

UCIe (Universal Chiplet Interconnect Express) was developed to solve specific issues posed by chiplet-based systems. It defines an open, standardized die-to-die connector designed for short-range, high-density communication within a package. UCIe provides very high bandwidth, minimal latency, and considerably higher energy efficiency than board-level interfaces. It can carry PCIe, CXL, streaming data, and proprietary protocols, with dedicated sideband channels for connection management and control. By focusing solely on intra-package needs, UCIe allows chiplets to communicate as if they were part of a single monolithic die, while preserving modularity and vendor compatibility.

Putting It Together: PCIe Outside, UCIe Inside

Modern CPU designs increasingly use a layered connection approach. UCIe interconnects compute tiles, memory chiplets, I/O dies, and accelerators with tight coupling and great efficiency. Outside of the packaging, PCIe provides a defined interface to the larger system, enabling expansion and compatibility with previous systems. This division also provides clarity in terms of verification and system design. UCIe verification focuses on latency, bandwidth efficiency, and sideband behavior in a controlled environment, whereas PCIe testing prioritizes robustness, compliance, and interoperability across several systems. Each connection is designed specifically for its domain, avoiding needless complexity.

Conclusion

As semiconductor design grows more modular and heterogeneous, interconnects play an increasingly important role in system performance and scalability. The future of chip designs does not include replacing PCIe with UCIe, but rather utilizing each when appropriate. As silicon modularizes, interconnects become the architecture, with PCIe outside the box and UCIe within the package defining the future.